Intelligent professional IP camera SoC

Overview

Allwinner V851S is a new generation of high-performance H.264/H.265 encoding SoC targeted for the field of IP Camera. It integrates single Cortex-A7 core@900MHz, RISC-V@600MHz, and 0.5 Tops NPU, and also supports various intelligent application such as human detection and crossing alarm. Allwinner V851S is designed with a new generation of high-performance ISP image processor and video encoder with professional encoding quality, low encoding bit rate and mainstream-level image processing capability. In addition, Allwinner V851S supports 64MB DDR2 and rich peripheral interfaces, such as USB, SDIO, and Ethernet, to meet the requirements of various IP Camera products.

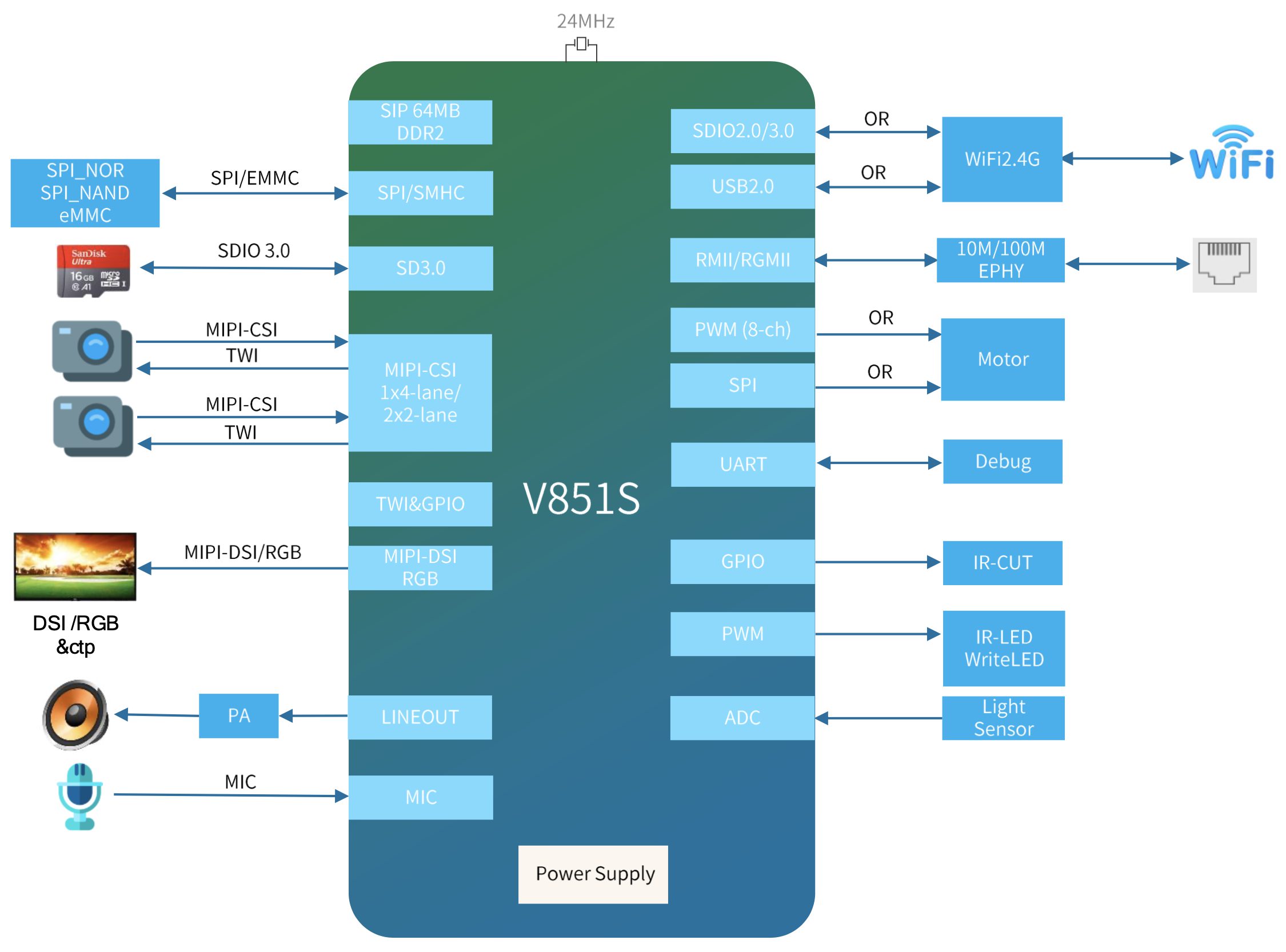

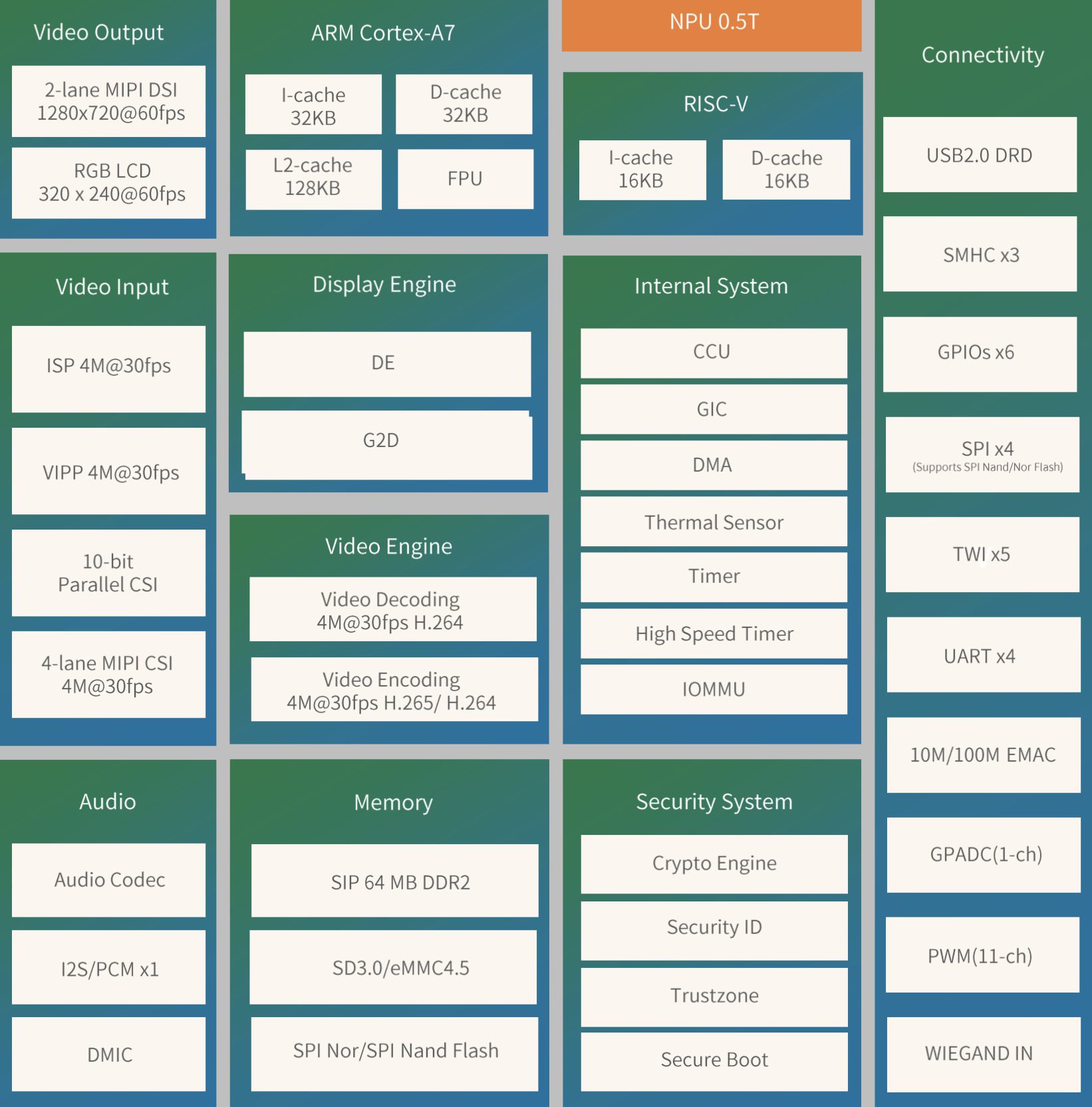

Block diagram

Specifications

CPU

Cortex-A7@900MHz CPU core, supporting 32 KB I-cache, 32 KB D-cache, and 128 KB L2 cache

RISC-V@600 MHz core, supporting 16 KB I-cache and 16 KB D-cache

NPU

Maximum performance up to 0.5 Tops

Embedded 128KB internal buffer

Support deep learning frameworks: TensorFlow, Caffe, Tflite, Pytorch, Onnx NN, etc

Memory

SIP 64 MB DDR2

SD3.0/eMMC 4.5 interface

SPI Nor/SPI Nand Flash

Video encoder

H.264/H.265 up to 4M@30fps

JPEG up to 1080p@60fps

Video decoder

Support H.264 BP/MP/HP, JPEG

Real-time multiple streams H.264 encoding capability: 4M@30fps

JPEG snapshot performance of 1080p@60fps independently

Display engine

Allwinner SmartColor post processing for an excellent display experience

Support 2 video channels and 1 Ul channel

Support G2D hardware accelerator including rotate, mixer, and scaler functions

Video out

RGB LCD output interface up to 320 x 240@60fps

1*2-lane MIPI DSI interface up to 1280x720@60fps

Audio

1 DAC and 1 ADC

Analog audio interfaces: MICIN1P/N, LINEOUTP

Digital audio interfaces: 12S/PCM x 1, DMIC x 1

Security system

AES, DES, 3DES encryption and decryption algorithms

RSA/ECC signature verification algorithm

MD5/SHA and HMAC tamper proofing

PRNG/TRNG hardware random number generator

Integrated 2 Kbits OTP storage space

Connectivity

USB2.0 DRD, SDIO 3.0, SPI X 4, UART X 4, TWI X 5, WIEGAND IN

PWM (11-ch), GPADC (1-ch)

10/100 M EMAC with RMII interfaces

Video input

ISP

- Maximum performance of 4M@30fps and maximum resolution of 2560x1440

- Support 3A (AE, AWB, and AF, parameters adjustable), 3DNR, and 2F-WDR

- Provide ISP tuning tools for the PC

- Support Lens Distortion Correction (LDC) and Fish Eye Correction (FEC)

VIPP

- Four VIPP YUV422 or YUV420 outputs

- Maximum performance of 4M@30fps and maximum resolution of 2560x1440

10-bit parallel CSI interface

- Maximum video capture resolution up to 4M@30fps

1x4-lane MIPI CSI interface

- Support DOL WDR mode and splitting into 2*2-lane MIPI CSI

- Support 4-ch VC de-interleaver function

- Maximum video capture resolution up to 4M@30fps

Package

QFN88, 9 mm x 9 mm body size, 0.35 mm ball pitch

Application diagram