Cost-effective IPC SoC

Overview

Allwinner V821 is a highly integrated low-power multi-camera IPC SoC, featuring dual RISC-V architecture processors. It supports real-time dual-camera input and provides 1080P high-definition video processing capabilities with internal high-performance ISP and H.264 encoder. Additionally, Allwinner V821 integrates Wi-Fi, LDO, IRCUT, and audio codec, offering a highly cost-effective IPC solution. With its excellent ISP processing performance, low power consumption, and high scalability, Allwinner V821 can be applied in multi-camera IPCs, low-power doorbells, smart locks, and other products.

Highlights

Simplified peripherals

Wi-Fi, LDO, IRCUT, and other IPC peripherals are integrated internally.

Real-time dual-camera input

Switch-free input with 1080P resolution for binocular product support, such as gun-ball linkage camera, door locks featuring face/palm vein recognition, peephole, etc.

Low power consumption

Support Keep-Alive mode (180μA@4.2V, DTIM10) for Wi-Fi router, also provide AOV low power solution.

Simplified development

One Linux SDK supports both normal-boot and fast-boot, also provide mass production solutions.

Simplified mass production

One firmware for both IPC SoC and Wi-Fi MCU burning.

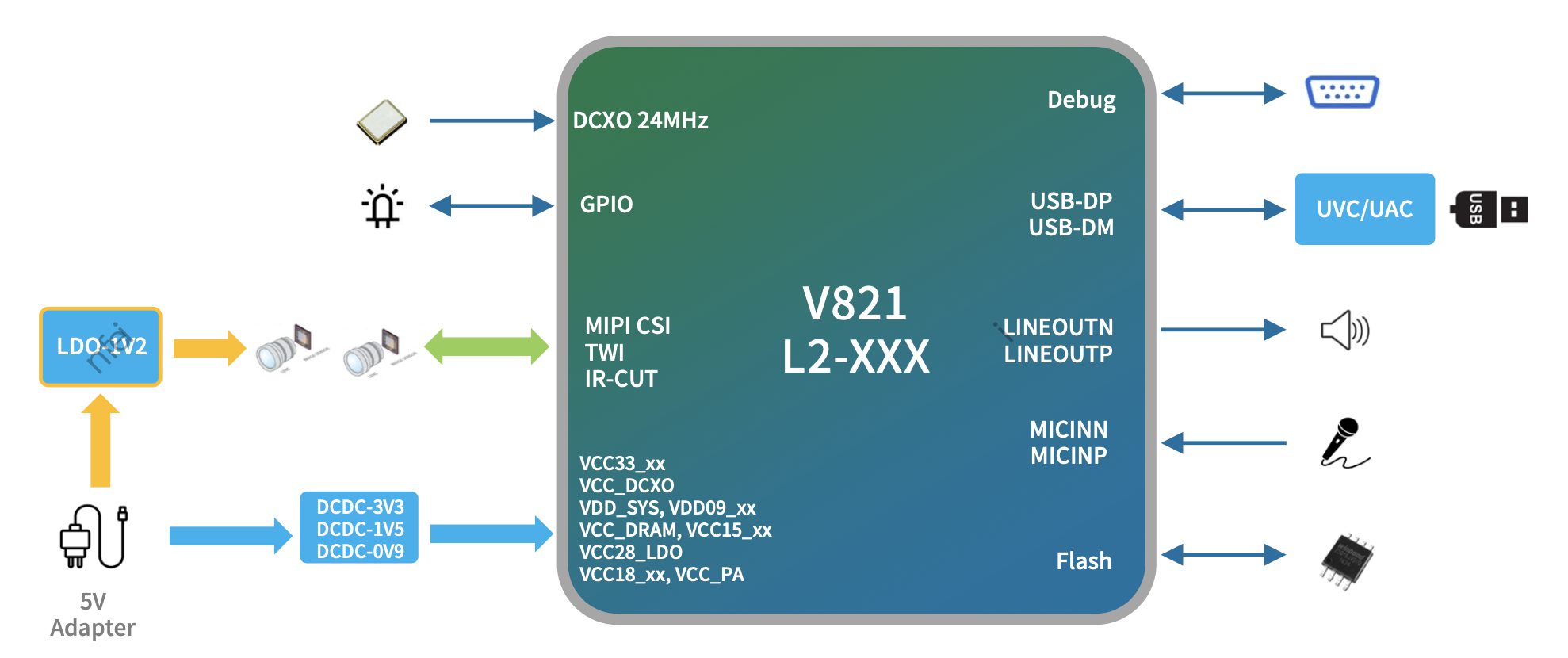

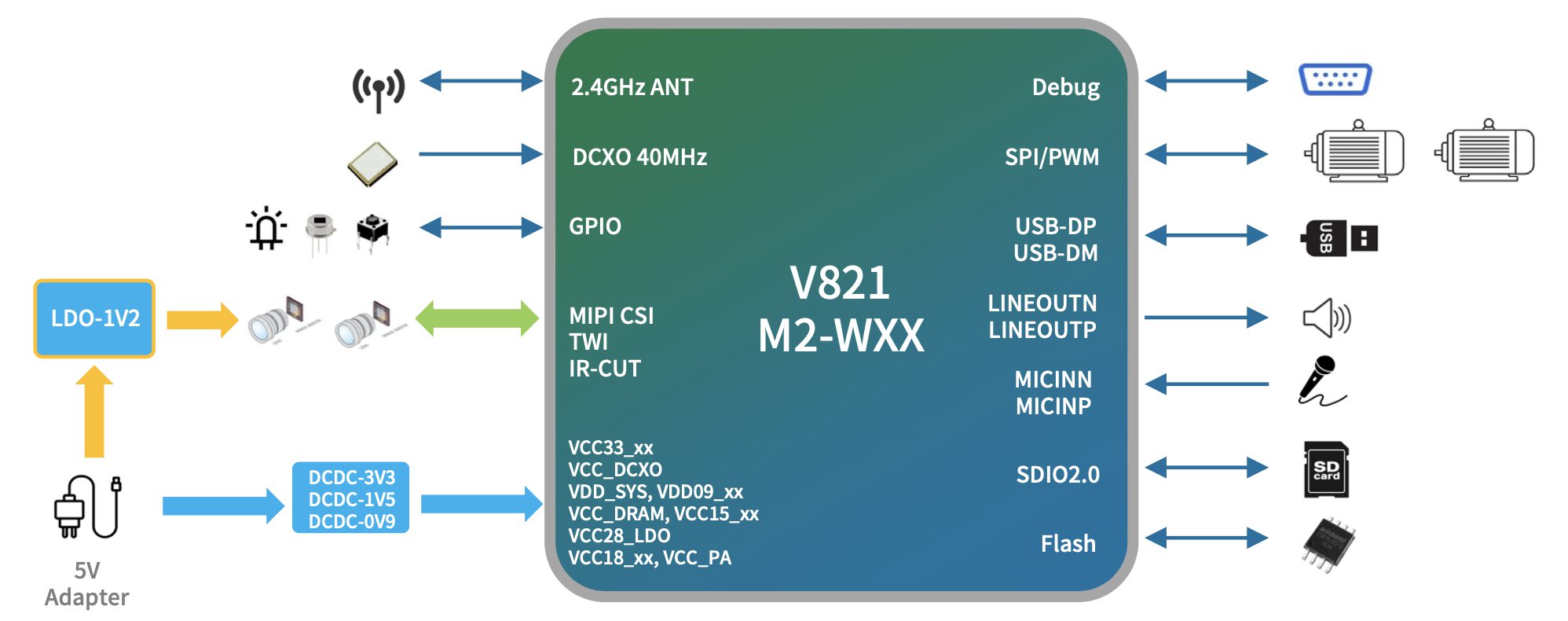

Block diagram

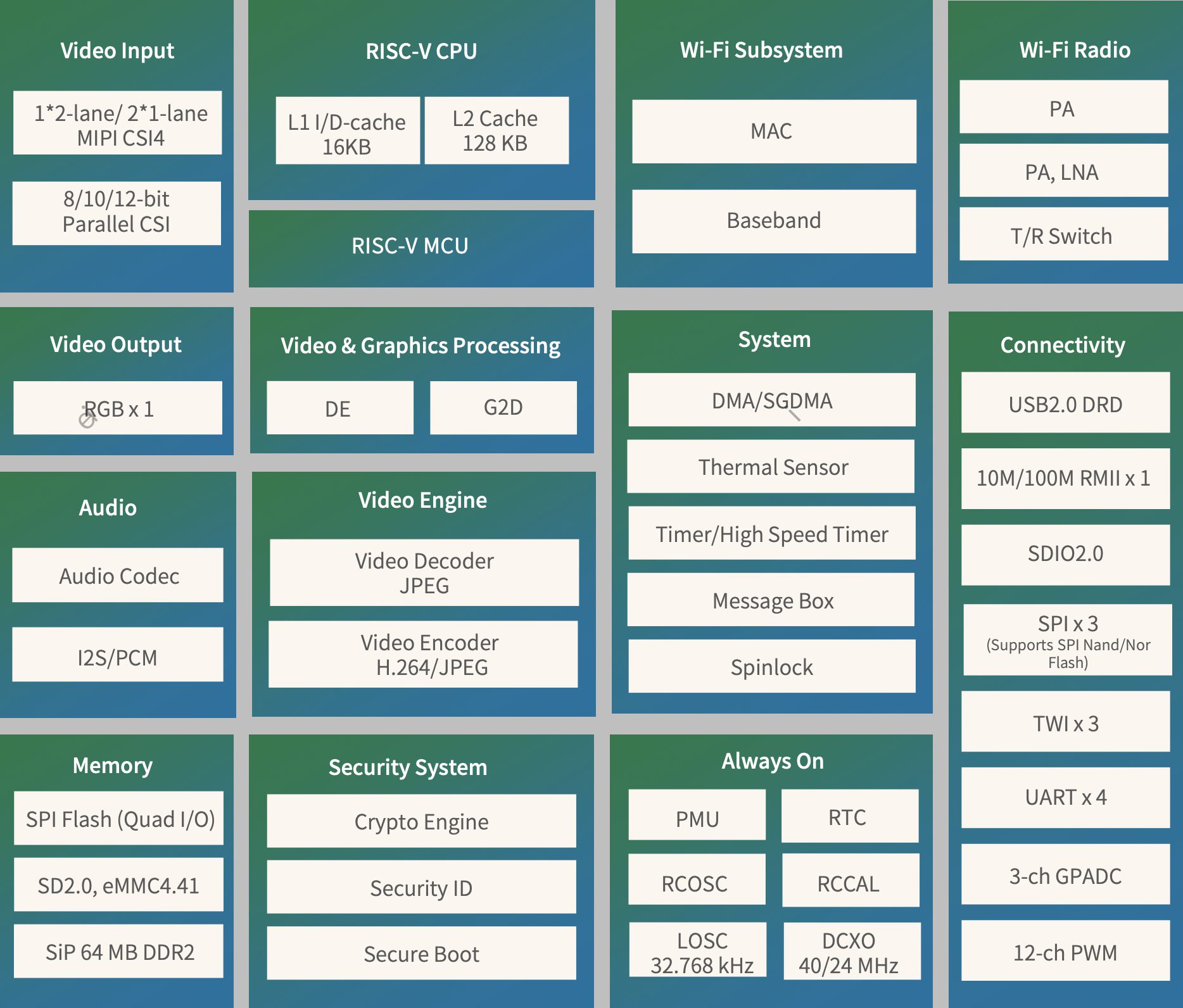

Specifications

Processor core

RISC-V CPU, up to 1 GHz

‐ 16 KB I-cache , 16 KB D-cache, 128 KB L2 cache

‐ Support dedicated operators for acceleration: Conv, Depthwise Conv, MaxPool, Add, Concat, etc

RISC-V MCU, up to 600 MHz

Video encoding/decoding performance

H.264 BP/MP/HP encoding

‐ Support I/P frame

‐ Maximum resolution: 3072 x 3072

Multi-stream real-time encoding capability

- Single-camera: 1920x1080@30fps + 640x480@30fps

- Dual-camera: 1920x1080@15fps*2 + 640x480@15fps*2

JPEG encoding/decoding

‐ Maximum resolution: 8192x8192

‐ Maximum performance: 1920x1080@60fps

Rate control modes: CBR, VBR, FIXQP, and QPMAP

Encoding of 8 ROIs

On-screen displaying (OSD) overlay pre-processing for 64 regions

Support simultaneous operation of H.264/MJPEG encoding and MJPEG decoding

Video output (for L2-WXX)

One RGB interface

‐ Serial/dummy RGB mode, up to 800 x 480@60fps

‐ i8080 interface, up to 800x480@60fps

Video input

1*2-lane/2*1-lane MIPI CSI

‐ Up to 1.0 Gbit/s per lane

‐ Compliant with MIPI-CSI2 V1.1 and MIPI DPHY V1.0

‐ Maximum resolution: 1920x1920

8/10/12-bit width parallel CSI interfaces

BT.656, BT.601, and Digital Camera (DC) protocol

BT.656 up to 2*720P@30fps

ISP

Sensor input supports up to 3456 x 1920 resolution

3A (AE, AWB, AF), parameters adjustable

Time Division Multiplexing (TDM) mode and maximum 2-lane multiplexing

Defect Pixel Correction (DPC) and lens shading correction

Local tone mapping

Multi-level noise reduction (spatial-domain noise reduction and time-domain multi-frame noise reduction), remove colour noise

Colour adjustment and colour enhancement

4 channels of scaling output from 1/16x to 1x

Provide ISP adjustment tool for the PC (online/offline/remote debugging)

Video & graphics processing

One video channel and one UI channel

Video channel supports 1/16x to 32x scaling

0/90/180/270 degree(s) picture rotation

Horizontal and vertical flip

Audio

1 DAC and 1ADC

1 x audio input: MICINP/N

1 x audio output: LINEOUTP/N

Embedded 1 I2S/PCM interface, supporting maximum 16 channels, 8 kHz-384 kHz sample rate, and 8-bit to 32-bit width

Security

AES, DES, and 3DES encryption and decryption algorithms

MD5 and SHA256 tamper proofing

160-bit hardware pseudo random number generator (PRNG) with 192-bit seed

128-bit hardware true random number generator (TRNG)

Integrated 2048-bit eFuse for chip ID and security application

WiFi

Compatible with IEEE 802.11b/g/n standard

Single-band 2.4 GHz 1T1R mode

Integrated LNA, PA, and T/R switch

Security support for WPA/WPA2/WPA3 personal and WPS2.0

Support STA, SoftAP, STA+SoftAP, and monitor modes

Power consumption (for L2-WXX)

Hibernation: 10 μA @4.2 V

Standby: 120 μA @4.2 V

Wi-Fi DTIM with external 32.768 kHz XTAL

‐ DTIM1: 650 μA @4.2 V

‐ DTIIM3: 300 μA @ 4.2 V

‐ DTIM10: 180 μA @ 4.2 V

Memory

Embedded 64 MB DDR2

SD2.0, eMMC4.41, and SPI NOR/NAND Flash for boot

One SPI interface, supporting quad DTR mode

Peripherals

1 x USB2.0 DRD, supporting UAC/UVC protocol

3 x SPI, 3 x TWI, 4 x UART

1 x 10/100 Mbit/s Ethernet port with RMII interface

12-ch PWM, 3-ch GPADC

Package

QFN88,9 mm x 9 mm

Application diagram

Wi-Fi binocular gun-ball linkage IPC

Face recognition module