Smart control and display SoC

Overview

Allwinner T113 is an advanced application processor. It integrates dual-core Cortex-A7 CPU, RISC-V, and single-core HiFi4 DSP to provide highly efficient compute power. Allwinner T113 supports full format decoding such as H.265, H.264, MPEG-1/2/4, and JPEG. The independent hardware encoder can encode in JPEG or MJPEG. Integrated multi ADCs/DACs and I2S/PCM/DMIC/OWA audio interfaces can provide excellent voice interaction solution. Allwinner T113 comes with extensive connectivity to facilitate product expansion, such as CAN, USB, SDIO, EMAC, TWI, UART, SPI, PWM, GPADC, IR TX&RX, etc.

The following is the Allwinner T113 family differentiated features.

| Feature | T113-S2 | T113-S3 | T113M3010DC0 | T113M4020DC0 | T113M4030DC0 | T113-i |

| RISC-V | Not Supported | Not Supported | Supported | Supported | Supported | Supported |

| DSP | Not Supported | Supported | Supported | Supported | Supported | Supported |

| DDR | SIP DDR2 64MB | SIP DDR3 128MB | SIP DDR3 128MB | SIP DDR3 256MB | SIP DDR3 256MB | External DDR |

| Package | eLQFP 128

14mm x 14mm |

eLQFP 128

14mm x 14mm |

eLQFP 128

14mm x 14mm |

eLQFP 128

14mm x 14mm |

eLQFP 128

14mm x 14mm |

LFBGA 337 balls

13mm x 13mm |

| LRADC | Not Supported | Not Supported | Not Supported | Not Supported | Not Supported | 1-ch |

| GPADC | 1-ch | 1-ch | 1-ch | 1-ch | 1-ch | 2-ch |

| Audio | MICIN3P/N

FMINL/R LINEINL/R HPOUTL/R |

MICIN3P/N

FMINL/R LINEINL/R HPOUTL/R |

MICIN3P/N

FMINL/R LINEINL/R HPOUTL/R |

MICIN3P/N

FMINL/R LINEINL/R HPOUTL/R |

MICIN3P/N

FMINL/R LINEINL/R HPOUTL/R |

MICIN1P/N MICIN2P/N MICIN3P/N

FMINL/R LINEINL/R LINEOUTLP/N LINEOUTRP/N HPOUTL/R |

| 2 x I2S | 2 x I2S | 2 x I2S | 2 x I2S | 2 x I2S | 3 x I2S | |

| MIPI DSI | Up to 720P@60fps | Up to 1920x1200@60fps | Up to 1920x1200@60fps | Up to 1920x1200@60fps | Up to 1920x1200@60fps | Up to 1920x1200@60fps |

| Video decoding | Up to 1080P@60fps | Up to 1080P@60fps | Up to 1080P@60fps | Up to 1080P@60fps | Up to 1080P@60fps | Up to 4K@30fps |

Highlights

Integrate dual-core Cortex-A7, RISC-V, single-core HiFi4 DSP, DDR, 3 ADCs, 2DACs, I2S/PCM, and 8 digital microphones, providing excellent voice interaction solution

H.265 full format decoding and Allwinner SmartColor 2.0 display enhancement technology, providing outstanding video experience

Rich display output interfaces such as RGB/LVDS/DSI/CVBS OUT meeting the requirements of screen display in differentiated markets

Advanced process design with lower voltage and lower leakage, power optimisation design for typical scenes, and enhanced heat dissipation package for better heating experience

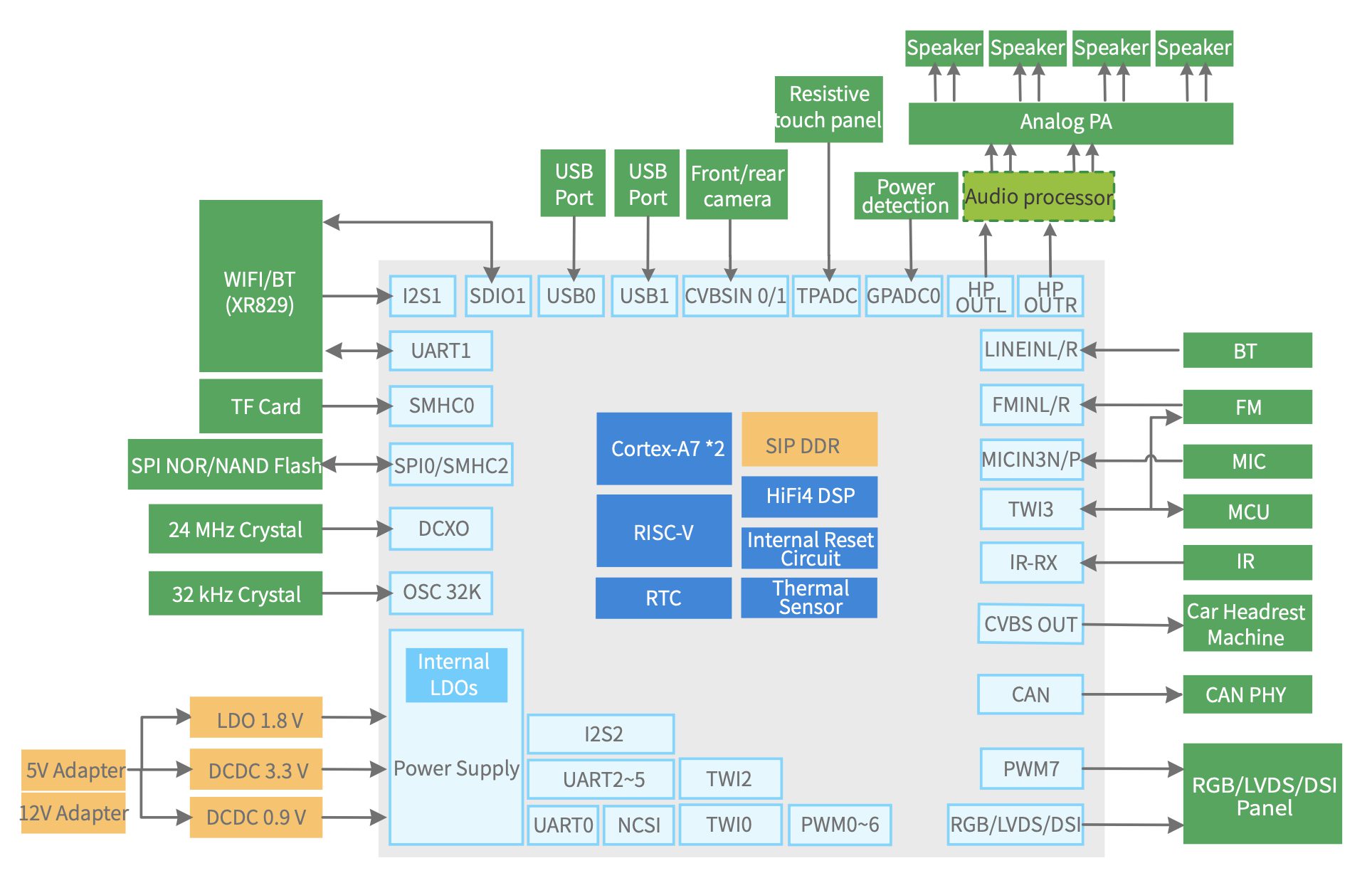

Block diagram

Specifications

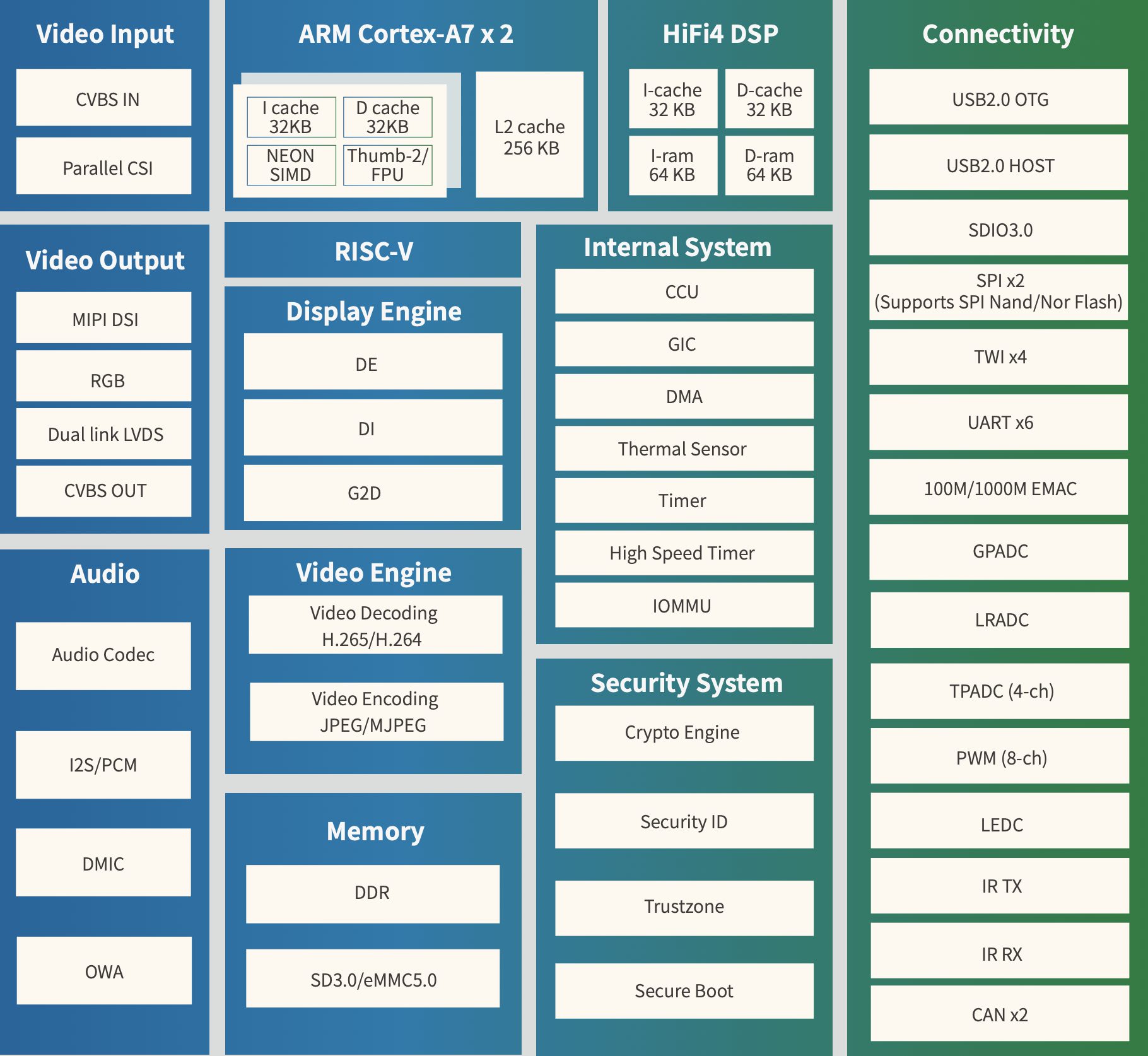

CPU

Dual-core ARM CortexTM-A7

- 32 KB L1 I-cache + 32 KB L1 D-cache per core, and 256 KB L2

RISC-V CPU

- 32 KB I-cache + 32 KB D-cache

DSP

Single-core HiFi4

- 32 KB I-cache + 32 KB D-cache

Memory

DDR

SD3.0/eMMC 5.0, SPI Nor/NAND Flash

Video decoding

H.265, up to 4K@30fps (for T113-i), 1080p@60fps (for others)

H.264, up to 4K@30fps (for T113-i), 1080p@60fps (for others)

H.263, MPEG-1/2/4, JPEG, Xvid, Sorenson Spark, up to 1080p@60fps

Video encoding

JPEG/MJPEG up to 1080p@60fps

Support input picture scaler up/down

Display engine

Allwinner SmartColor2.0 post processing for excellent display experience

Support de-interlace (DI) up to 1080p@60fps

Support G2D hardware accelerator including rotate, mixer, lbc decompression

Video OUT

CVBS OUT interface, supporting NTSC and PAL format

RGB LCD output interface up to 1920 x 1080@60fps

Dual link LVDS interface up to 1920 x 1080@60fps

4-lane MIPI DSI interface up to 1920 x 1200@60fps

Video IN

8-bit parallel CSI interface

CVBS IN interface, supporting NTSC and PAL format

Audio

2 DACs and 3 ADCs

Analog audio interfaces:

- MICIN1P/N, MICIN2P/N, MICIN3P/N, LINEINL/R, LINEOUTLP/N, LINEOUTRP/N, FMINL/R, HPOUTL/R (for T113-i)

- MICIN3P/N, FMINL/R, LINEINL/R, HPOUTL/R (for others)

Digital audio interfaces: I2S/PCM, DMIC, OWA

Security system

AES, DES, 3DES encryption and decryption algorithms

RSA signature verification algorithm

MD5/SHA and HMAC tamper proofing

Hardware random number generator

Integrated 2 Kbits OTP storage space

Connectivity

USB2.0 OTG, USB2.0 Host

SDIO 3.0, SPI x 2, UART x 6, TWI x 4, CAN x 2

PWM (8-ch), GPADC, LRADC (only for T113-i), TPADC (4-ch), IR TX&RX

10/100/1000M EMAC with RMII and RGMII interfaces

Package

LFBGA 337 balls, 13mm x 13 mm (for T113-i)

eLQFP 128, 14mm x 14mm (for others)

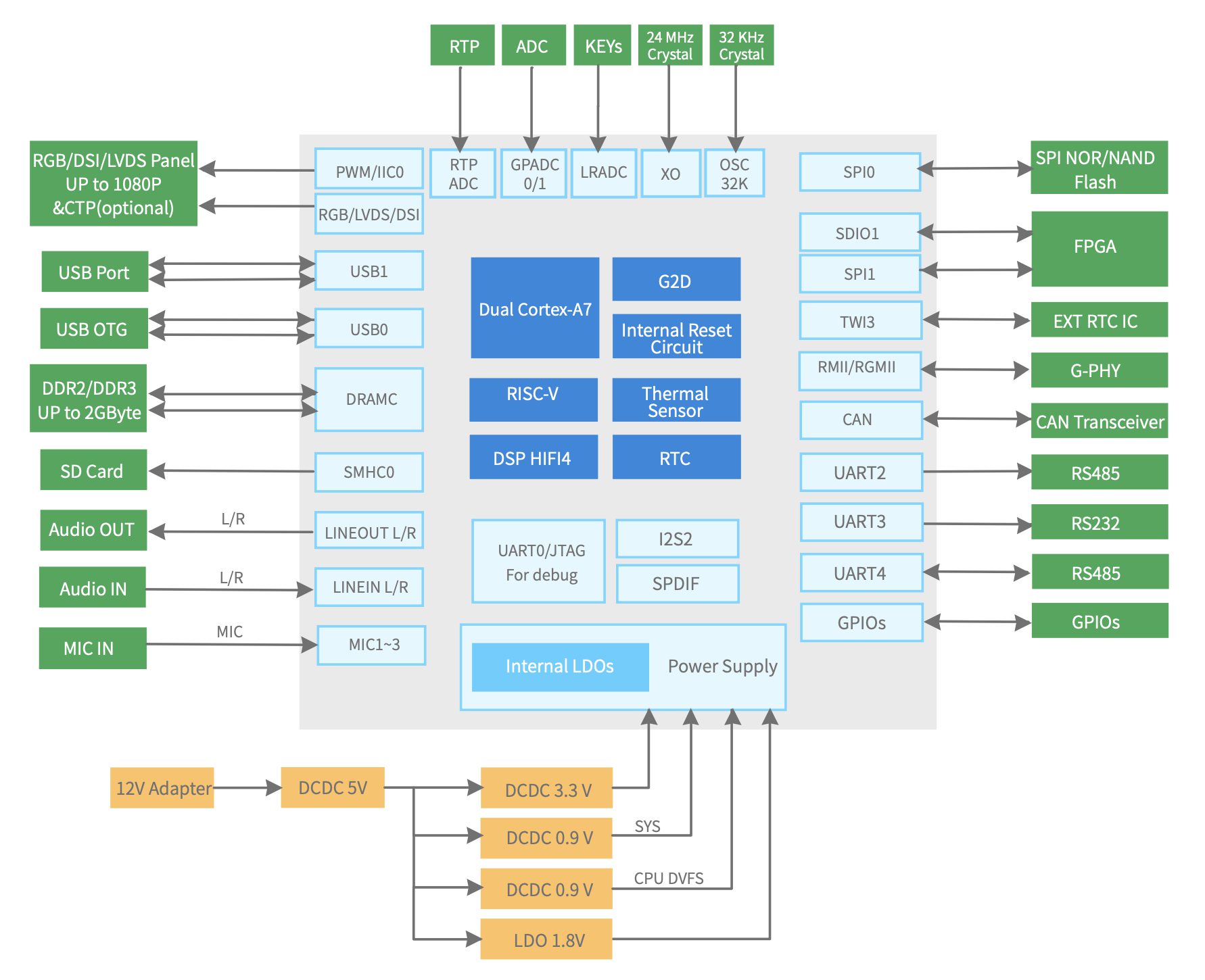

Application diagram

The following diagram is for chips other than T113-i.

The following diagram is for T113-i only.